我们提到大家常会用半导体产业链指代芯片产业链,更准确来说,二者所指向的其实是半导体芯片产业链。那在本篇内容里,我们就专门讲清楚半导体产业里的“C位担当”—— 半导体芯片产业链。

半导体芯片产业链是个高度复杂且分工精细化的产业体系,按照上中下游的产业逻辑可划分为:

上游是半导体生产材料、生产设备及设计工具等支撑性领域。

中游是最为核心的芯片制造环节,包括芯片设计、晶圆制造和封装测试三大工序。

下游则是消费电子、计算机、汽车等芯片等终端应用方。

半导体芯片产业链示意图

为了大家更透彻地理解产业链,这次讲解产业链我们不按从上游切入的惯例,而是从中游切入,先拆解芯片制造最核心的三个环节(芯片设计、晶圆制造、封装测试),再一一解析每个环节背后的上游支撑要素。

【中游环节1】芯片设计:给芯片“画图纸”

芯片设计,又被称为IC设计,这个环节就像是盖房子前的设计规划,设计好芯片的“施工图纸”。

目前,芯片设计主流采用“自顶向下”的设计思路(Top-Down),需要经过规格设计、架构设计、逻辑设计、物理设计四个关键步骤,但实际操作过程非常复杂,设计周期通常需要1-3年甚至更长的时间,要知道一颗 CPU里集成的晶体管数量可达上百亿级别,有极高的设计难度。

→芯片设计对应的上游环节

支撑芯片设计的上游主要是 EDA 软件和 IP 服务。

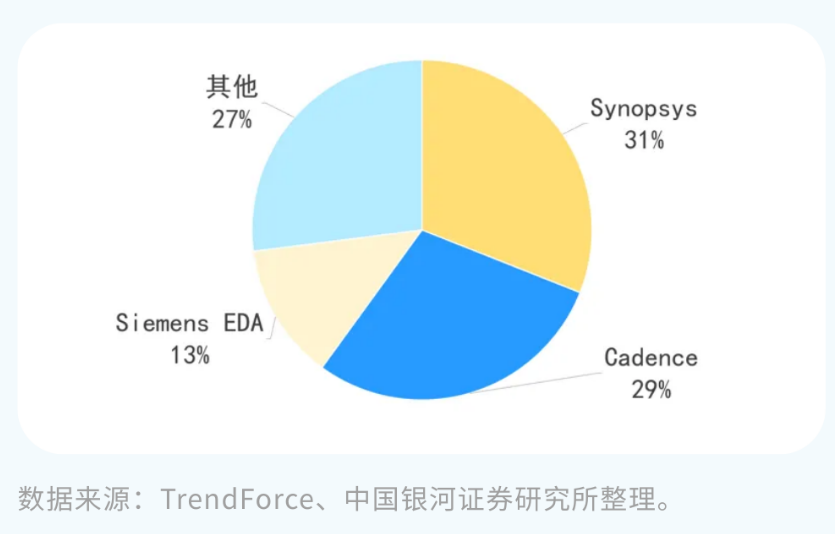

EDA(电子设计自动化)软件是芯片设计的必备工具,从集成电路的逻辑设计、仿真验证到布局布线,均需依赖其完成,是设计效率的决定性因素,其全球市场被Synopsys、Cadence、Siemens EDA三大厂商主导,虽然国内也有一些EDA企业,但市场份额较小,EDA软件仍是半导体领域的“卡脖子”环节。

2024年全球EDA市场竞争格局

IP 服务则是预先设计好的、可复用的设计模块(如CPU核、高速接口IP等),企业可直接通过采购并集成这些模块来实现某项功能,能有效避免重复劳动、缩短设计周期。

【中游环节2】晶圆制造:硅片上“建城市”

如果说设计是 “画图纸”,那晶圆制造就是按图施工“建城市”,将设计好的电路图案转移到晶圆上,通过一系列精密的工艺,打造出芯片的层层立体结构。

要在晶圆上造成芯片,首先需要制备晶圆,晶圆通常是指由高纯度单晶硅制成的圆形薄片,需要将石英砂经过高温提纯、拉单晶硅、切割、化学机械抛光(CMP)等多个环节的处理,最终形成晶圆。

接下来便进入芯片前道工艺阶段,这是芯片加工制造的核心环节,流程精密且复杂,大致步骤是:

1. 对晶圆表面进行氧化处理,形成一层二氧化硅保护膜;

2. 涂覆光刻胶,再通过光刻机将掩模上的电路图案精准投射到晶圆表面;

半导体光刻示意图

3. 经刻蚀工艺去除未被光刻胶保护的材料;

4. 通过离子注入技术掺入杂质,构建PN结;

5. 之后采用薄膜沉积技术形成金属互连层、绝缘层等薄膜层。

上述步骤需循环数十次甚至上百次,中间还需要多次清洗、抛光。整个晶圆制造步骤就像建房子一样,一层层建上去,最终搭建起复杂的立体架构。

已完成前道工艺的晶圆示意图

→晶圆制造对应的上游环节

支撑晶圆制造的上游可以分为晶圆制造材料和晶圆制造设备两大块,价值密度极高,部分关键核心技术是我国正在下大力气寻求突破的领域。

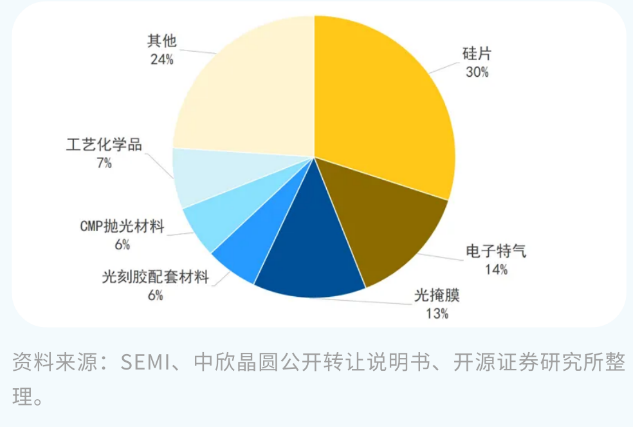

第一,晶圆制造材料方面,需用到硅片(晶圆制造的基底材料)、光刻胶(与光刻机配合,通过化学反应将掩膜版上的图形转移到硅片上的关键材料)、电子特种气体(氧化、还原、除杂等)、光掩膜(为光刻提供图案投射模板)等,其中 EUV光刻胶、高纯度电子级硅材料等关键材料技术门槛极高。

从市场结构看,硅片、电子特气和光掩膜占据了主要规模。

2024年半导体晶圆制造材料全球市场规模占比

第二,晶圆制造设备方面,光刻机、刻蚀机、薄膜沉积设备等是重要组成部分,市场规模占比大、技术难度高、价值高,尤其是EUV光刻机全球仅荷兰ASML公司能商用量产,全球先进芯片厂(如台积电)均需依赖其EUV设备。

2024年半导体晶圆制造设备全球市场规模占比

资料来源:拓荆科技,SEMI,方正证券研究所。

半导体芯片产业链的环节繁多、覆盖面广,受限于篇幅,更多半导体芯片产业链的内容,敬请关注“一文贯通半导体芯片全产业链”下篇!

声明:本资料仅用于投资者教育,不构成任何投资建议。我们力求本资料信息准确可靠,但对这些信息的准确性、完整性或及时性不作保证,亦不对因使用该等信息而引发的损失承担任何责任,投资者不应以该等信息取代其独立判断或仅根据该等信息做出决策。基金有风险,投资须谨慎。

本资料版权为易方达基金所有,所载文字、数据和图表等未经易方达基金书面许可,任何单位或个人不得以转载、复制、改编、二次创作等任何形式使用本资料。对于任何侵犯本资料版权的行为,易方达基金将保留依法追究侵权者法律责任的权利。